今天去高雄參加婚禮 ,現在整個呈現疲憊狀態 Orz

還好我有先把今天的文章預先打好不然就要開天窗拉~~

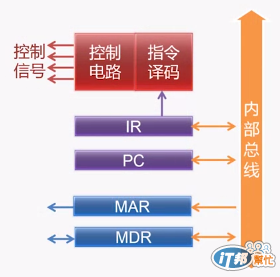

今天再來看看 CPU 上半部的控制器

控制器用於控制計算機各元件完成取址、分析和執行等功能

主要組成元件如下:

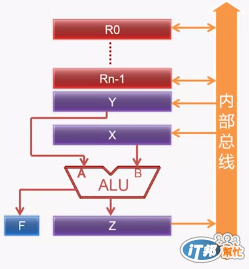

接下來是運算器的部分

運算器當然是用於完成運算的,至於運算可以被分成算術和邏輯兩種

常見算術運算有加減乘除,邏輯運算就是not、and、or 等等

運算器主要核心元件就是 ALU(Arithmetic Logic Unit) ,用於完成算術運算和邏輯運算

由圖可以看到他有兩個輸入一個輸出

例如加法中的加數和被加數分別從 A 端口和 B 端口輸入

經過 ALU 運算後將結果送到輸出端口

為了方便描述,我們將 ALU 的輸入和輸出分別設計了三個暫存器 XYZ ,

也就是說 ALU 會對 XY 中的數據進行運算,並且將結果存到Z當中

F(Flag) 則是用來存放運算結果的狀態,例如零、正負號、進位、或是 overflow

R0~Rn-1 是 n 個通用的暫存器,用於存放臨時的數據

這些數據可能來自於存儲器、其他通用暫存器、或是 ALU 的輸出。

內部匯流排(總線)

剛剛提到的各種通用暫存器、 ALU 、或是控制器中的暫存器之間是怎麼傳遞數據的呢?

這時候就需要內部匯流排的協助。

內部匯流排是用於在 CPU 中的各元件之間傳遞數據,

而至於具體是怎麼實現的,課程後面在上電路實現時會提到。

不過老師舉了例子

他說可以將暫存器想像成一個一個蓄水池,有各自的進出水口,透過內部總線這個水管連接

當你要將數據從 R0 傳到 X,就等於是把 R0 的出水口和 X 的進水口打開,其他都關掉

這樣水就會嘩啦嘩啦地從 R0 流到了 X

雖然這讓我疑惑的是 X 的水不就變成 R0 和 X 的總和了嗎

但是只是類比,應該只是先想像一下那個感覺別細究內容的意思吧XD

那到此為止這個計算機結構的簡化模型就構造完成囉

下一篇將會觀察這個模型的動態運行過程。